# Fascicle-Selective Ultrasound-Powered Bidirectional Wireless Peripheral Nerve Interface IC

Jianxiong Xu, Student, IEEE, José Sales Filho, Student, IEEE, Sudip Nag, Member, IEEE,

Liam Long, Student, IEEE, Eugene Hwang, Camilo Tejeiro, Gerard O'Leary, Yu Huang, Mustafa Kanchwala,

Mohammad Abdolrazzaghi, Chenxi Tang, Patty Liu, Yuan Sui, Hao You,

Xilin Liu, Member, IEEE, José Zariffa, Senior Member, IEEE, and Roman Genov, Senior Member, IEEE

Abstract—This paper presents an innovative, minimally invasive, battery-free, wireless, peripheral nervous system (PNS) neural interface, which seamlessly integrates a millimeter-scale, fascicle-selective integrated circuit (IC) with extraneural recording and stimulating channels. The system also incorporates a wearable interrogator equipped with integrated machinelearning capabilities. This PNS interface is specifically tailored for adaptive neuromodulation therapy, targeting individuals with paralysis, amputation, or chronic medical conditions. By employing a neural pathway classifier and temporal interference stimulation, the proposed interface achieves precise deep fascicle selectivity for recording and stimulation without the need for nerve penetration or compression. Ultrasonic energy harvesters facilitate wireless power harvesting and data reception, enhancing the usability of the system. Key circuit performance metrics encompass a 2.2 µVrms input-referred noise, 14-bit ENOB, and a 173 dB Schreier figure of merit (FOM) for the neural analogto-digital converter (ADC). Additionally, the ultra-low-power radio-frequency (RF) transmitter boasts a remarkable 1.38 pJ/bit energy efficiency. In vivo experiments conducted on rat sciatic nerves provide compelling evidence of the interface's ability to selectively stimulate and record neural fascicles. The proposed PNS neural interface offers alternative treatment options for diagnosing and treating neurological disorders, as well as restoring or repairing neural functions, improving the quality of life for patients with neurological and sensory deficits.

*Index Terms*—peripheral nervous system, neural interface, battery-free, wireless, adaptive neuromodulation, fascicleselective, wearable interrogator, machine learning, in vivo, circuit performance, ultra-low-power RF transmitter, neural ADC.

# I. INTRODUCTION

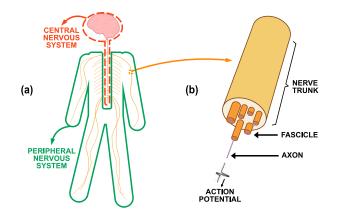

The peripheral nervous system (PNS) plays a critical role in our body's overall function, working in tandem with the central nervous system (CNS). The PNS serves as a communication channel between organs and the CNS, as shown in Fig. 1(a) [1]. PNS neural interfaces have been employed to restore motor or sensory functions in individuals with paralysis or amputation and as implantable therapeutic devices for treating chronic medical conditions related to autoimmune or metabolic disorders. However, their efficacy and clinical use scope is limited due to the invasiveness of the cable, electronics, and battery and the lack of nerve fascicle selectivity and online adaptivity [2].

J. Xu, J. Filho, S. Nag, L. Long, C. Tejeiro, G. O'Leary, Y. Huang, M. Kanchwala, M. Abdolrazzaghi, C. Tang, P. Liu, Y. Sui, H. You, X. Liu, R. Genov are with the Department of Electrical and Computer Engineering, University of Toronto, Toronto, ON M5S 3G4, Canada. E. Hwang, J. Zariffa are with the Institute of Biomedical Engineering, University of Toronto, Toronto, ON M5S 3G9, Canada. (contact: jianxiong.xu@mail.utoronto.ca)

1

Fig. 1. (a) Illustration of a connection between the central nervous system and the peripheral nervous system, (b) Cross-sectional representation of a peripheral nerve, showcasing its internal structure.

Figure 1(b) depicts the cross-section of a typical nerve. Within the nerve trunk, fascicles containing bundles of axons serve as conduits for neural action potentials or electrical signals. Fascicles undergo a continuous process of division and branching, with each fascicle containing axons directed towards multiple targets. Consequently, an interface specifically designed for individual fascicles can offer superior functional selectivity compared to a whole-nerve interface due to this inherent anatomical complexity. Therefore, fascicles are frequently the primary targets for recording and stimulation in PNS interfaces. Nerves are complex neural structures, for example, the vagus nerve houses approximately  $10^4$  axons in mice and an order of magnitude higher in humans [3]. This nerve connects to several vital organs, necessitating selective recording to distinguish neural pathways related to specific organ functionalities. Selective nerve stimulation is also essential to avoid triggering undesired neural activity in unintended pathways.

PNS stimulation has emerged as a promising approach for the treatment of various conditions, including neurological disorder treatment [4], as well as restoring motor/sensor functions [5]. Notably, peripheral nerve stimulation has been found effective in the treatment of epilepsy [6], the management of chronic migraine [7], and chronic pain treatment [8].

For instance, in the context of neural disorder treatment, vagus nerve stimulators have been developed as a treatment for drug-resistant epilepsy [6]. These devices periodically

2

stimulate the vagus nerve using electrical stimuli, which in turn affects the brain and results in suppressing seizures. Despite their potential, these devices face limitations in terms of efficacy and may cause increased side effects for the patient. This is because the entire vagus nerve is stimulated, affecting all connected brain regions, rather than only affecting the specific brain location involved in causing seizures. One approach to address this issue is to enhance stimulation selectivity by targeting specific fascicles within the nerve trunk that exclusively interact with the focal seizures location in the brain.

In another example, in cases of restoring motor/sensor functions [9]–[11] where patients experience motor impairments due to conditions such as amputations or spinal cord injury (SCI), the motor intentions persist within the motor cortex. In the context of amputations, a PNS neural interface is instrumental in recording from the PNS to decode motor intentions, and in stimulating the PNS to elicit sensations in the user. This is noteworthy as both functionalities occur above the level of the amputation. Conversely, in SCI, the PNS neural interface is utilized differently. It can stimulate the PNS to evoke movement and can record from the PNS to extract sensory information, which subsequently serves as a feedback signal for the closed-loop control of stimulation. These functions are happening below the level of the lesion.

The aforementioned two examples show that selective recording and stimulation of peripheral nerves are essential for the advancement of implantable PNS-interfacing bioelectronic therapeutic devices as needed to improve neural disorder treatment efficacy. However, existing PNS neural interfaces require nerve penetration to achieve selectivity, such as intraneural [12] and regenerative [6], [13] interfaces, with such nerve invasiveness posing significant challenges to their long-term stability and potential harm to nerves. Ideally, PNS neural interfaces should be extraneural while still achieving high levels of selective stimulation and recording (i.e., the extraneural recording/stimulation is favored over intraneural and regenerative approach).

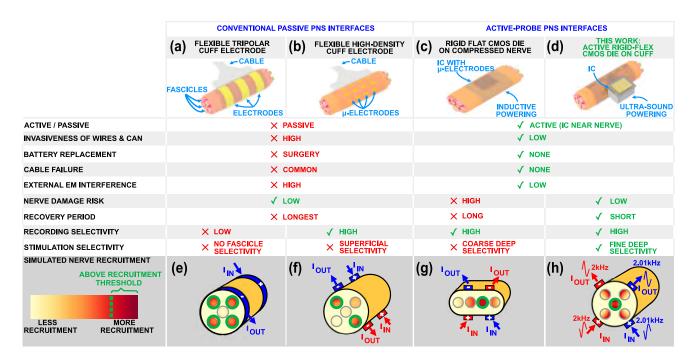

To address these challenges, we present a battery-free wireless PNS interface that features a mm-scale fascicle-selective neural interface IC with extraneural recorders and stimulators, as well as a wearable interrogator with integrated machine learning (ML) to enable adaptive neuromodulation therapy with low invasiveness. The proposed PNS interface is designed to facilitate fascicle selectivity in both recording and stimulation without penetrating or compressing the nerve, utilizing ultrasonic energy harvesting for wireless power delivery. This paper expands upon our initial brief report in [2]. In this paper, we expand on it and offer a comprehensive discussion of the biomedical facets of our work. This includes an analysis of (1) the architecture of the PNS neural interface, (2) the design methodologies and experimental validation for wireless data communication and power supply, (3) the realization and verification of fascicle-selective stimulation, and (4) the development and evaluation of machine learning algorithms that facilitate selective neural recording for the differentiation of various neural pathways. Figure 2 provides a summary of existing and the proposed PNS neural interfaces (top),

alongside the advantages and disadvantages associated with each interface (middle) and the stimulation methods (bottom) employed for each.

The system's key performance metrics include a neural analog-to-digital converter (ADC) with a  $2.2\mu$ Vrms inputreferred noise, 14-bit effective number of bits (ENOB), and a 173 dB Schreier figure of merit (FOM), as well as 1.38 pJ/bit energy efficiency for the ultra-low-power radio frequency (RF) transmitter. In vivo experiments on the rat sciatic nerve further highlight the interface's selective recording and stimulation capabilities on neural fascicles. The proposed system holds significant potential for various applications, including but not limited to the treatment of drug-resistant epilepsy and the restoration of sensorimotor functions.

This paper is organized to provide a comprehensive and coherent understanding of the proposed PNS neural interface, its development process, and potential applications. The structure of the paper is as follows. Section II delves into the background of existing PNS neural interfaces, offering an in-depth analysis of their strengths and weaknesses. In Section III, we discuss the architecture of the proposed PNS neural interface, exploring its essential components. Section IV focuses on the individual circuit blocks that constitute the system, offering a detailed examination of their design methods, functionalities, and contributions to the overall objectives of the proposed PNS neural interface. In Section V, we report the results of in vivo experiments performed to evaluate the efficacy of the proposed PNS neural interface. Section VI presents a comparative analysis, positioning the proposed PNS neural interface in the context of existing solutions within the field. Finally, Section VII concludes the paper.

## **II. PNS NEURAL INTERFACES**

The preceding discussion highlights the function of the PNS and the importance of performing selective recording and stimulation of peripheral nerves. This section introduces performance metrics to evaluate the effectiveness and usability of PNS neural interfaces and presents case studies of conventional passive PNS neural interfaces and the emerging active PNS neural interfaces, discussing their respective advantages and disadvantages. Lastly, our proposed PNS neural interface is presented, which addresses various requirements and challenges associated with existing PNS neural interfaces. To comprehensively evaluate a PNS neural interface, the following performance metrics shall be considered, and are also listed in Fig. 2(left).

Active or Passive: This parameter refers to the placement of recording channels in proximity to the recording site, which influences the signal-to-noise ratio (SNR) of the neural interface. Passive interfaces transmit raw electrical signals from the nerve to a distant recording/stimulation instrument via cable, with the SNR being dependent on factors such as cable impedance, and other variables such as electromagnetic interference (EMI) from external sources (described in detail later in this list) and cross-talk between adjacent channels. In contrast, active neural interfaces digitize neural signals at the recording site and transmit only the digitized data, rendering

Fig. 2. Comparative analysis of peripheral nerve electrical interfaces. (a-d) Interface with a peripheral nerve trunk by means of: (a) passive tripolar cuff electrode, (b) passive high-density cuff electrode, (c) inductively powered rigid flat CMOS-die active electrode, and (d) ultrasound-powered rigid-flex active electrode. (e-h) Simulated nerve recruitment for: (e) passive tripolar cuff electrode, (f) passive high-density cuff electrode, (g) rigid flat CMOS die active electrode, and (h) rigid-flex active electrode.

the SNR reliant solely on the quality of the recording channel and substantially reducing the impact of factors that degrade SNR in passive interfaces.

**Invasiveness:** The level of invasiveness in a neural interface directly influences the likelihood of complications, the degree of patient discomfort, and the stability of the interface over an extended period. Solutions that minimize invasiveness, such as those eliminating wires and the implant "can", are generally favored in order to reduce the associated risks and improve patient outcomes.

**Battery Replacement:** The requirement for battery replacement surgeries may constrain the long term usability of a neural interface. A system featuring extended battery life or alternative power sources is considered more advantageous, as it reduces the need for additional surgical interventions.

**Cable Failure:** Dependence on cables can present potential failure points within the system. Implementing cable-free or wireless alternatives can mitigate this concern, thereby enhancing the overall reliability and robustness of the system.

**Electromagnetic Interference (EMI):** EMI on cables can compromise the quality of recorded neural signals and disrupt stimulation. A well-designed interface ought to minimize EMI to guarantee accurate and reliable data acquisition and stimulation.

**Nerve Damage Risk:** Minimizing nerve damage risk through extraneural implantation approaches is preferable to ensure safety and long-term efficacy. A carefully designed neural interface should be capable of recording high-quality action potentials in axons from the surface of the nerve trunk without penetrating or compressing the nerve trunk.

Recovery Period: Reduced recovery periods subsequent to

surgical procedures serve to alleviate patient discomfort and minimize interruptions to their daily routines. As such, it is essential that the interface be designed with a compact form factor, ideally resulting in minimal open wounds during the implantation process.

**Recording Selectivity:** Enhanced recording selectivity facilitates the interface's ability to discriminate between various neural fascicle and pathways, thus enabling the acquisition of more precise and comprehensive information.

**Stimulation Selectivity:** An interface with high stimulation selectivity is crucial for delivering precise stimuli to the specific target fascicle without affecting other fascicles. This accuracy ensures that only the desired neural pathways are activated, enhancing the overall effectiveness of the therapeutic intervention.

The aforementioned requirements constitute the main challenges and considerations for PNS interfaces, and a successful design should tackle these concerns. Furthermore, depending on the specific application, additional requirements may arise. An effective neural interface must accommodate the primary requirements and application-specific demands. In certain cases, trade-offs may exist between these requirements, necessitating the achievement of a balance to optimize overall performance and functionality for the interface.

## A. Conventional passive PNS interfaces

Figure 2(a) illustrates conventional passive PNS interfaces with the tripolar cuff recording electrode configuration [14], [15]. The ring contact of the electrode wraps around the entire nerve trunk, recording action potentials from all fascicles. For neuro-stimulation, two ring contacts of a bipolar (or

tripolar) cuff electrode deliver electrical stimuli, activating all fascicles (highlighted in green) surrounded by the ring contact, as depicted in Fig. 2(e). This configuration suffers from poor fascicle selectivity, affecting the overall recording and stimulation spatial resolution and efficacy. Additionally, it exhibits a suboptimal performance matrix due to using passive electrodes and the high invasiveness arising from long cables. Electromagnetic interference and cable interference can significantly diminish recording and stimulation performance. The recovery period following implantation may be extended due to the invasiveness of the surgery, as the form factor of the passive electrode along with the cables and the "can" could be quite large. However, it offers some advantages, such as causing minimal nerve damage, as it wraps around the nerve without nerve trunk penetration or compression.

Figure 2(b) presents a passive high-density flexible nerve cuff electrode, which offers improved selectivity compared to the tripolar cuff electrode discussed earlier [16]. The use of high-density fine grid contacts for recording facilitates selective recording, as each contact is more likely to record neural activity in its vicinity. Figure 2(f) depicts a basic stimulation configuration utilizing a passive high-density flexible nerve cuff electrode, wherein two pairs of electrodes are chosen to deliver biphasic current pulses to the nerve. In this instance, the superficial fascicles (highlighted in green) in proximity to the active stimulation contacts are activated, resulting in enhanced selectivity compared to the tripolar cuff electrode that activates all fascicles near the ring contact. Despite these advancements in selectivity, these interfaces exhibit similar drawbacks as tripolar cuff electrodes, such as high invasiveness, a need for battery replacement, and an extended recovery period. They also remain susceptible to electromagnetic interference and stimulation crosstalk, which can undermine the quality and reliability of PNS neural interfaces. These interfaces typically engage superficial nerve fibers, further limiting their application scope. Similarly to the tripolar cuff electrode configuration, they do not inflict substantial nerve damage, as they envelop the nerve without penetration or compression.

## B. Active PNS interfaces

Figure 2(c) depicts the active probe configuration for PNS neural interfaces, as proposed in [17] and [18]. That design involves flip-chip bonding an integrated circuit to a FINEstyle [19] electrode cuff, positioning the electrode contacts on two opposite sides of the nerve. The direct attachment of the chip to the nerve substantially improves the signalto-noise ratio (SNR) of the active probe, resulting in enhanced neural recording accuracy. Figure 2(g) illustrates the selective stimulation capabilities of this active probe, wherein intersectional short pulses [20] are applied to opposite-side contact pairs to build up the average charge density in localized regions within the nerve trunk while maintaining a low charge density elsewhere. In this simplified example, two biphasic current sources are activated sequentially, delivering charges that individually are below the nerve's recruitment threshold at the surface. The additive total current in the middle facilitates a charge build-up that exceeds the recruitment threshold of the

fascicle (highlighted in green) near the center of the nerve. Furthermore, the wireless functionality of this active probe reduces invasiveness by obviating the need for cables and mitigating related complications, such as cable replacement and electromagnetic interference. A key feature of this active probe is its ability to access deeper fascicles via nerve compression, which enables selective deep-fascicle recording through nerve reshaping. Nonetheless, such deformation is inadvisable for critical nerves, such as the vagus nerve, as compression can result in prolonged nerve recovery time and may cause permanent nerve damage if excessive.

Figure 2(d) presents the proposed PNS interface designed to attain deep fascicle selectivity without the need for nerve penetration or compression. The proposed design incorporates the chip onto the rigid section of a flexible-rigid electrode array substrate. The flexible electrode array conforms to the nerve's shape, effectively wrapping around it to minimize the risk of nerve damage. By situating the recording system in close proximity to the recording site, the signal-to-noise ratio is enhanced, and the effects of electromagnetic interference are mitigated, ultimately improving the overall performance of the interface. A distinguishing feature of this device is its fully wireless operation, enabled by ultrasonic power transmission. This approach permits deeper implantation of the device, eliminates the need for cumbersome battery cables, and reduces the invasiveness of the implantation procedure. Additionally, the proposed design employs a convolutional neural network (CNN) neural pathway classifier (discussed in section IV.D) as well as the temporal interference stimulation paradigm, as shown in Figure 2(h) and elaborated upon in Section IV.B. While the concept of temporal interference stimulation has been previously explored for brain interfaces [21], its application to peripheral nerves is an innovative aspect of our work. For finer-scale selective stimulation on the targeted nerve, our approach is visualized in green in Figure 2(h).

In summary, our proposed battery-free wireless PNS interface was designed to address these challenges head-on. The key novelties and improvements over conventional interfaces include: (1) battery-free operation - by leveraging ultrasonic power transfer, our design eliminates the need for battery replacements, thus reducing the invasiveness and potential for complications, (2) wireless connectivity - The absence of cables in our system minimizes potential failure points, thereby boosting the system's reliability, (3) minimized EMI - Without cables, our system experiences minimal EMI, ensuring the integrity of recorded neural signals, (4) safety-centric Design - Our neural interface prioritizes nerve safety, focusing on high-quality recordings without nerve damage, (5) compact design - Our system's compact form factor facilitates a reduced recovery period for patients.

## **III. SYSTEM-LEVEL ARCHITECTURE**

Previously, we introduced the various requirements for PNS neural interfaces. This section presents the system-level architecture of the proposed design of our fascicle-selective peripheral nerve interface.

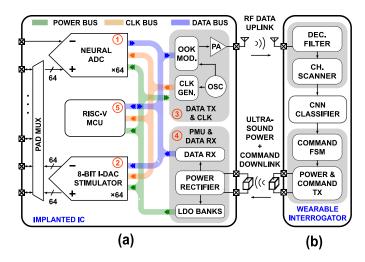

Figure 3(a) depicts the system-level block diagram of the proposed IC, comprising: (1) an array of 64 neural analog-

Fig. 3. Block diagram of the presented: (a) PNS neural interface integrated circuit architecture, and (b) its wearable interrogator.

to-digital converters (ADCs) designed for high-density neural activity monitoring and responsible for amplifying and digitizing peripheral nerve signals for subsequent processing; (2) an array of 64 8-bit current-mode neuro-stimulators tailored for temporally interfering focal stimulation; (3) a wireless data transmitter (TX) and a clock generator, facilitating the uploading of recorded data to the wearable interrogator and generating on-chip clock signals, respectively; (4) a wireless power management unit (PMU) and a data receiver (RX) for harvesting ultrasound power and receiving commands from the wearable interrogator, respectively; and (5) a RISC-V processor included for optional on-chip data handling and processing. The entire system's nominal power consumption amounts to only 480  $\mu$ W.

Figure 3(b) illustrates the interrogator components: (1) a decimation filter employed for neural data pre-processing, responsible for filtering high-frequency quantization noise; (2) a channel scanner for extracting temporal and spatial features essential for classification; (3) a convolutional neural network (CNN) dedicated to real-time neural pathway classification, determining rodent's limb movement types based on the previously extracted features; (4) a finite-state machine (FSM) generating commands for chip control; and (5) power and command TX components designed to send ultrasound power and data transmission to the chip, respectively.

The closed-loop operation of the proposed PNS neural interface comprises several sequential steps. First, the raw neural signals recorded and digitized by the neural ADC are transmitted to the interrogator through a data uplink. The low power consumption of the transmitter allows it to send all data to the off-chip interrogator for analysis, consuming significantly less power than employing an on-chip digital classifier [22] or other advanced-technology analog hardware accelerators [23], [24].

Second, the interrogator carries out digital signal processing and identifies distinct neural pathways using a convolutional neural network-based (CNN) classifier. Based on the classification results, commands are then transmitted to the stimulator via a data downlink. This process facilitates the delivery of electrical stimuli to the subject according to the specific requirements dictated by the information obtained from the identified neural pathways.

Our proposed PNS neural interface is designed to operate in a closed-loop manner, aiming to continually optimize and adapt electronic neuromodulation therapies to cater to the unique physiological responses of each patient. The closedloop system achieves this by actively monitoring neural signals and adjusting stimulation parameters in real-time. This dynamic approach promises to elevate the treatment's overall effectiveness by ensuring more targeted and efficient neuromodulation, thereby offering potential advancements in managing various neurological conditions.

## IV. CLOSED-LOOP FUNCTIONAL BLOCKS

In the preceding section, our emphasis was placed on elucidating the design considerations and methodologies pertaining to the system architecture. In this section, we concentrate on examining the circuit-level design, offering an in-depth analysis of the design strategies and considerations for each functional block present in both the implantable integrated circuit (IC) and wearable interrogator.

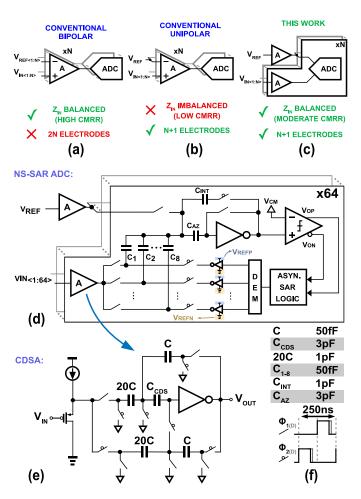

## A. Neural ADC

Conventionally, neural amplifiers use either the bipolar (as shown in Fig. 4(a)) or the more popular unipolar (as shown in Fig. 4(b)) recording configuration, which typically suffer from a high number of electrodes or from imbalanced input impedance significantly degrading the common-mode rejection ratio (CMRR), respectively. To maintain the minimum number of electrodes and a moderate PNS-suitable CMRR, we introduce a pseudo-differential configuration with matched input impedance by using an additional preamplifier for the reference input (as shown in Figs. 4(c,d)).

Each preamplifier is a switched-capacitor correlated-doublesampling amplifier (CDSA) that reduces low-frequency noise and offset, as shown in Fig. 4(e). A source-follower buffers the CDSA's input and sets the low-pass frequency corner. A selfbiased near the cut-off region, the inverter amplifier replaces a conventional OTA to reduce static power consumption. A 1st-order noise-shaping (NS) SAR ADC with such an inverterbased integrator samples the pre-amplified neural signal and reference differentially to enable common-mode rejection, as depicted in Fig. 4(d). The oversampling NS SAR ADC provides significantly higher SNDR than the Nyquist rate ADC or the non-uniform sampling ADC [25].

Figure 4(f) shows the capacitor sizes and the clock phases for the switches used in the proposed analog front-end. During phase  $\Phi_1$ , the two CDSAs amplify the potential difference between the neural signal and the reference, which is then buffered on the ADC's sampling capacitors; during phase  $\Phi_2$ , the CDSAs sample the dynamic offset and the low-frequency noise, while the ADC converts the sampled signal through  $\Phi_1$  to a digital code using asynchronous SAR logic. Dynamic element matching (DEM) is employed to reduce the impact of the mismatch in the capacitor bank. The front-end achieves

Fig. 4. Electrode connection configurations: (a) bipolar differential; (b) unipolar differential; and (c) unipolar pseudo-differential. The presented unipolar pseudo-differential analog front-end implementation: (d) noise-shaping SAR ADC schematic; (e) correlated-double-sampling amplifier (CDSA) schematic; and (f) clock phases for switches used in the presented analog front-end.

an input-referred noise of 2.2  $\mu$ Vrms over a 2.5 kHz band with noise efficiency factors (NEFs) of 2.55 and 3.93, without and with the ADC power included, respectively. The ADC achieves an effective number of bits (ENOB) of 14 bits and a Schreier figure of merit (FOM) of 173dB. The choice of the 14-bit resolution was made to balance the need for high SNDR and high power efficiency. The total area of the AFE is 0.02mm<sup>2</sup>.

# B. Multi-channel I-DAC for temporal interference neuro-Stimulation

Inspired by the recently discovered temporal interference stimulation (TIS) method for deep brain stimulation [21], our proposed approach applies TIS to peripheral nerves. To the best of our knowledge, this is the first work that utilizes the TIS method for focused stimulation of peripheral nerves.

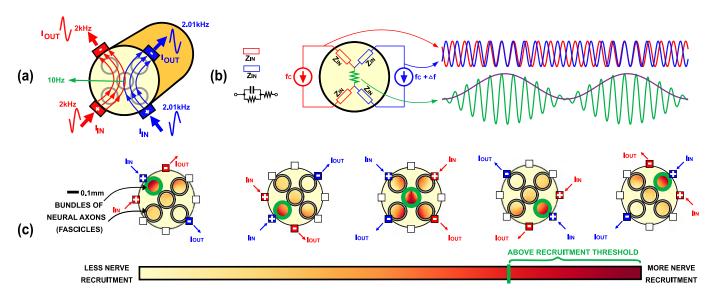

The operating principle of TIS is illustrated in Figure 5(a), which demonstrates the delivery of a temporally interfering electric field deep within a nerve without the need for nerve penetration or compression. In this cross-sectional view of a nerve, two pairs of stimulation electrodes from a high-density cuff electrode array are used. Two differential high-frequency

current stimulation signals, within the kHz frequency range and with a small frequency difference of  $\Delta f$ , are applied to two selected pairs of electrodes in the cuff electrode array. This results in generating two electric fields,  $E_1$  and  $E_2$ , highlighted in red and blue, respectively. The interference between these fields creates an intermodulation field, with  $\Delta f$  emerging as the frequency of the resulting interference envelope.

Since nerves are responsive in a low-frequency band where  $\Delta f$  resides, one can activate the desired deep fascicles without affecting most other fascicles in the nerve. By adjusting the stimulating signal parameters to generate fields interference at different location of cross section of the nerve, it becomes possible to selectively target deep fascicles.

Figure 5(b) presents a circuit-based analysis method to illustrate the TIS principle. The electrode and tissue interface is modeled using a lumped components model,  $Z_{\rm IN}$ , which consists of a resistor in parallel with a capacitor and a series resistor. The fascicle situated in the middle of the nerve is modeled by a resistor, highlighted in green. Two differential current sources are connected to two pairs of electrodes at the nerve's surface, where the red current source has a frequency of  $f_c$ , and the blue current source has a frequency of  $f_c + \Delta f$ .

Utilizing the superposition method for circuit analysis, the current flowing through the green resistor is evaluated for each current source. The total current (the green waveform) is the sum of the red and blue currents, resulting in a modulation envelope of the low-frequency  $\Delta f$  (the purple waveform), also known as the beat frequency. In this example, the beat frequency is largest in the center region of the nerve and diminishes elsewhere. By altering the strength of each current source and the choice of stimulation electrode pairs, selective targeting of different fascicles within the nerve bundle can be achieved.

Figure 5(c) displays a color map generated from a finiteelement simulation demonstrating the electric field distribution within a nerve model and the selective stimulation capability of the TIS method. From the left to the right in Fig. 5(c), The top left, bottom left, center, bottom right, and top right fascicles are stimulated, respectively. Specific nerve regions can be targeted to achieve fields above the desired recruitment threshold by selecting the appropriate electrode pairs to stimulate along the high-density cuff electrode array.

Overall, our proposed TIS-based approach for peripheral nerve stimulation offers several advantages, including eliminating the need for a high-voltage CMOS process [2] or the requirement for utilizing smaller electrodes, such as nerve-penetrating electrodes. Figure 6 presents a simplified schematic of the stimulator, which features a dual wide-swing current source architecture. This structure is designed to both push and pull current to/from the electrode, improving the output impedance of the current source. In order to attain an 8-bit resolution, we control the gate voltage of PMOS and NMOS transistors-sized in binary fashion-using 8 control bits. This approach enables selective activation or deactivation of the 8 binary-weighted current sources. Moreover, this method achieves deep nerve stimulation without compressing or penetrating the nerve, thereby reducing the risk of nerve damage. By providing an extraneural focused

JOURNAL OF XXXX, VOL. XXX, NO. XXX, XXX 2023

Fig. 5. Temporal interference stimulation (TIS) for peripheral nerves: (a) operating principle using a high-density cuff electrode array; (b) circuit analysis of TIS with lumped component models, and (c) finite-element numerical simulation demonstrating selective stimulation capability.

Fig. 6. Schematic of the proposed current neural stimulator.

stimulation method for peripheral nerves, this approach can potentially improve therapeutic outcomes, patient comfort, and overall safety. As neural interfaces evolve, integrating TIS into peripheral nerve stimulation systems represents a promising direction for advancing the field, fostering an improved understanding of neural function, and enhancing the development of targeted treatments for various neurological disorders. The neurostimulator is designed with a compliance voltage of 3.3V. The neurostimulator operates at a frequency of 2kHz, and considering the reduction in electrode impedance over frequency, the maximum deliverable peak-to-peak current is around 3mA. It is important to note that the current specifications are tailored for rat experiments and are not optimized for human applications.

# C. Edge-combining data uplink transmitter

In preceding sections, we examined the analog front-end architectures and the neuro-stimulation method, both essential for nerve interfacing. In this subsection, we will shift our focus to the data transmission component of the system, placing particular emphasis on our proposed design strategies and methods for the transmitter (TX) that are specifically tailored to accommodate the diverse requirements of neural implants and, more generally, of various other biomedical implantable devices.

1) Motivation: A significant challenge associated with the PNS neural interface involves enabling wireless multi-channel data transmission while maintaining ultra-low power consumption and small area usage and adhering to the preferable sub-GHz frequencies for low tissue attenuation.

The choice of the local oscillator (LO) is of paramount importance due to its substantial impact on the overall power budget for ultra-low-power (ULP) TXs. While inductorcapacitor voltage-controlled oscillator (LC-VCOs) are the standard power-efficient means of frequency synthesis, their large-area requirements at sub-GHz frequencies impede miniaturization. Conversely, ring oscillators (ROs) can achieve the minimum dimensions and a desirable large tuning range, but they consume power excessive for implant micro-power budgets.

To address the power consumption drawbacks of ROs, we propose a current-mode edge-combining (EC) technique aimed at attaining ULP for event-based TXs in micro-implants: a frequency-multiplying switching-current-ripple (FMIR) technique. This technique enables the synthesis of high-frequency carriers from slower, lower-power ROs through in-ring operation with minimal circuit overhead. The measurement results demonstrate the effectiveness of the RO EC technique, which can provide a sufficient carrier frequency for multi-channel data rates and direct-modulation architectures to enable dutycycled power on-off keying (OOK).

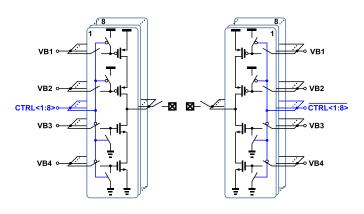

2) VLSI implementation: Figure 7(a) presents the frequency-multiplying current-ripple data transmitter (TX), utilizing a voltage-controlled oscillator power amplifier (VCO-PA) current re-use stacked TX solution. The design comprises three main components: (1) an edge-combining ring

Fig. 7. (a) Schematic representation of the frequency-multiplying currentripple data transmitter (TX) utilizing a VCO-PA current re-use stacked TX solution, consisting of an edge-combining ring oscillator (RO), a power modulator for OOK data modulation, and a stacked current-reusing commongate regulating power amplifier. (b) Illustration of the inverter relain switching dynamics, depicting the output voltage waveform at each inverter stage and the associated supply current spikes, that are used to time the data transmission at a higher frequency (Nf) than that of the VCO (f).

oscillator (RO) that serves as the core frequency generator; (2) a power modulator for OOK data modulation, which alternates the power amplifier and oscillator on and off; and (3) a stacked current-reused common-gate regulating power amplifier, responsible for amplifying the modulated data and setting the control voltage for the ring oscillator.

As illustrated in Fig. 7 (b, bottom), upon switching at a frequency of f, each inverter in the chain alternates between VDD and ground at f, charging and discharging its output load capacitance. This process results in considerably large supply current spikes at f, as shown in Fig. 7 (b, middle).

The inherent characteristics of the power-supply current in an inverter chain are exploited to reduce power consumption. The sequential switching of each inverter stage produces a train of equally spaced current spikes. When combined within a single period of the ring oscillator, these current spikes generate a high-frequency switching harmonic with an integer value equal to the number of stages, N. Consequently, the RO supply current  $I_A$  spikes are at a frequency  $f_A = f \times N$ , which is N times higher than the RO oscillation frequency. Finally, the RO supply current  $I_A$  flows into the LC load through a power amplifier, producing an N times higherfrequency voltage signal (as shown in Fig. 7 (b, top)) with an N-stage slower-operating ring oscillators, leading to the corresponding power savings. This design strategy enhances the overall efficiency and performance of the transmitter while maintaining its compact and low-power characteristics.

The generation of supply ripple-current is a fundamental aspect of edge-combining ring oscillator's operation. However, implementing these oscillators exclusively with CMOS transistors, sized to meet stage delay and ring frequency requirements, results in nonideal current waveforms that deviate from the simple model previously discussed. Device parasitic capacitances give rise to various phenomena and transient current profiles that differ from the anticipated train of sharp transient current spikes. Still, an LC-free, transistor-only ring oscillator (RO) implementation leads to minimal area usage, which can be advantageous in certain use cases.

Equation 1 shows a straightforward metric employed to assess the ring's efficiency in generating ripple currents.

$$\eta_{\rm ripple} = \frac{I_{\rm Apeak}}{I_{\rm DC}} \tag{1}$$

where  $I_{Apeak}$  is the peak amplitude of  $I_A$ , and  $I_{DC}$  is the power supply DC current flow through the ring oscillator.

The ripple-current-efficiency can be utilized for frequency synthesis purposes, such as minimizing  $\eta_{\text{ripple}}$  supply ripple for low-noise applications or maximizing  $\eta_{\text{ripple}}$  supply ripple for higher output power.

In our design, we aim to maximize  $\eta_{ripple}$  since phase noise does not significantly impact the bit error rate due to the use of OOK modulation. The most critical device parasitic factor impairing our  $\eta_{ripple}$  is the gate-to-drain parasitic capacitances of each inverter. Upon sharp switching at the input, these capacitances conduct input charge into the output node, resulting in an instantaneous sharp voltage step at the output with the same phase as the input signal. Consequently, this diminishes ripple spikes of adjacent RO stages and reduces the overall  $\eta_{ripple}$ .

One approach to mitigate this issue involves reducing transistor sizes, thereby lowering the parasitic capacitance  $(C_{gd})$ of devices and employing dedicated load capacitances at each output node to reduce the core oscillating frequency. This approach introduces a trade-off between area and efficiency.

An additional technique for maximizing  $\eta_{ripple}$  is based on inverter skewing. By enlarging the widths of PMOS transistors used in the inverter, their corresponding  $R_{on}$  and the inverter rise times decrease. As a result, peak currents charging load capacitances increase upon falling-edge switching. However, beyond a specific point, static leakage current becomes significant, further reducing  $\eta_{ripple}$ . Therefore, when designing the proposed current-mode edge-combining ring oscillator, the transistor size choices were based on the aforementioned tradeoffs.

For the FMIR-TX, OOK modulation is achieved using a simple power modulator in the power amplifier (PA) bias path. This modulator toggles the PA  $(M_1)$  on and off, controlling the current flow into the oscillator and thus activating or deactivating the oscillator.

In the context of FMIR current-output modulation onto the supply, the PA transistor  $M_1$  is required to fulfill two essential functions. Firstly, it must provide trans-impedance gain in the signal path, which facilitates the transduction of  $I_A$  to  $V_{OUT}$ . Secondly, it must achieve a certain level of load regulation to establish the control voltage,  $V_{CTRL}$ , enabling the oscillator to attain the desired oscillating frequency. These objectives must be met while preserving a low input impedance so as to absorb the majority of the  $I_A$  current emanating from the ring oscillator (RO). The minimization of  $R_{IN}$  for  $M_1$  and stage trans-impedance gain can be realized by maximizing  $g_{m1}$ .

An inherent negative feedback loop is present within the system structure, providing the necessary regulation by establishing  $V_{\rm CTRL}$ . The feedback loop can be analyzed as follows. When substantial switching currents are present, the  $V_{\rm CTRL}$

value decreases, which subsequently leads to an increase in  $V_{\rm gs}$  for  $M_1$ . As a result, a higher supply current is pumped into the ring oscillator, causing the  $V_{\rm CTRL}$  value to increase and, in turn, leading to a decrease in  $V_{\rm gs}$  for  $M_1$ . This phenomenon can be alternatively understood as a reduction in the regulator path's resistance, effectively bringing  $V_{\rm CTRL}$  closer to the oscillator's predetermined set point. This inherent negative feedback loop allows for stable and efficient regulation of the system, ensuring optimal performance in various operating conditions.

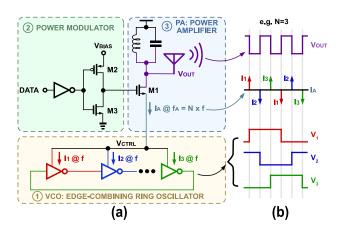

3) Testing setup and measurement results: Figure 8 presents the test setup and the key measurement results for the proposed frequency-multiplying current-ripple data transmitter (FMIR-TX). The test setup, as illustrated in Fig. 8(a), comprises the pseudo-random binary sequence (PRBS) generator, FMIR-TX, the TX antenna, the RX antenna, the matching network for both TX and RX and the power amplifier for the RX. These components have been carefully selected and arranged to ensure the accuracy and reliability of the measurements. A planar inverted-F antenna (PIFA) with a defected ground is used as the TX element in implant, and is designed on a low-cost FR4 substrate. The low dielectric constant of the substrate ( $\varepsilon_r = 4.5$ ) enables a moderate efficiency of 55% and a bandwidth of 17 MHz within a compact size. The antenna is folded to minimize the size for implantable and wearable applications while a shorted stub near the feeding point is used to match the antenna. Moreover, an ultra-wideband antenna (47% of its center frequency) is designed with circular polarization. This coplanar waveguide (CPW)-fed slot antenna incorporates two C-shaped slots at two opposite corners, which is crucial for circular polarization and makes it suitable for wireless communication. Reflection  $(S_{11})$  of both of these antennae are measured as shown in 8(d-e), which are in great agreement with the simulation results obtained from high frequency software HFSS. These results provide a comprehensive understanding of the antenna performance and its compatibility with the FMIR-TX.

Figure 8(f) illustrates the spectrum of the pseudo-random binary sequence on-off keying (PRBS-OOK) modulated signal, highlighting the FMIR-TX's ability to produce an accurate modulated output at a data rate of 20 Mbps. Furthermore, the continuous wave carrier spectrum received at the RX is depicted in Fig. 8(g), demonstrating the power available at the receiver end. These results showcase the effectiveness of the proposed transmission system in generating and receiving modulated signals. To address the antenna design procedure and efficiency in the sub-GHz data link, we conducted a series of simulations and experiments. The efficiency of the TX antenna was measured at 40% when placed 1mm away from rat skin with a thickness of 4mm. This efficiency further increased to 50% when the antenna and the skin were separated by a distance of 5mm. Additionally, a Specific Absorption Rate (SAR) analysis was performed. The results shown in Fig. 8(g) demonstrate that the average SAR over 10g of rat skin, when the antenna is fed by 1W of power, remains well below the safety standard of 1.6 W/kg. These findings confirm the suitability and safety of our antenna design for sub-GHz data transmission in this particular application.

9

Fig. 8. The testing setup and key experimental measurement results. (a) FMIR-TX testing setup. (b) The TX antenna used to test the FMIR-TX. (c) The RX antenna used to test the FMIR-TX. (d) The  $S_{11}$  parameter of the TX. (e) The  $S_{11}$  parameter of the RX. (f) Measured OOK modulated frequency spectrum using a PRBS. (g) Measured received carrier spectrum. (h) SAR Analysis of the TX Antenna.

The measurement results for the data transmitter reveal that the 5-stage edge-combining TX generates a radio frequency signal centered at the 915 MHz industrial, scientific, and medical (ISM) band. This frequency is achieved through frequency multiplication across each ring oscillator stage, utilizing a base RO operating frequency of only 183 MHz. The onoff keying modulated spectrum underscores the transmitter's performance, achieving a maximum data rate of 20 Mbps while maintaining low power consumption at 27.63  $\mu$ W. The system exhibits an energy efficiency of 1.38 pJ/bit at the maximum data rate.

In summary, our system incorporates an energy-efficient, frequency-multiplying OOK transmitter based on a currentmode edge-combining principle. Current ripples from each ring oscillator VCO stage are merged at the source of the NMOS transistor, which acts as a power amplifier. The proposed design allows for efficient frequency multiplication, directly contributing to the energy efficiency of the system. For an N-stage ring oscillator, the VCO frequency is multiplied by N. This approach not only enables energy-efficient frequency multiplication but also offers a wide tunable frequency range due to the inherent characteristics of the ring oscillator VCO. By leveraging this unique architecture, our system can deliver the desired performance while maintaining energy efficiency and adaptability to a wide range of operating conditions.

## D. CNN-based neural pathway classifier

1) Motivation: As previously discussed, the selective recording of peripheral nerves has become increasingly important in the advancement of bioelectronic systems. Extraneural techniques demonstrate the potential to enhance long-term stability, a crucial aspect for clinical applications. However, extraneural peripheral nerve recording still presents a significant challenge due to the low signal-to-noise ratios (SNR) when compared to their intraneural [12] and regenerative [6], [13] counterparts.

To tackle this issue, we a utilized convolutional neural networks (CNN) to associate naturally evoked compound action potentials (nCAPs) with specific neural pathways, leveraging spatiotemporal patterns found in multi-contact nerve cuff recordings. This algorithm builds on what initially proposed in [26] and implemented in hardware in [17] [18]. In the present work, we further optimize the algorithm to reduce the number of parameters and create a 420x smaller model size without significantly sacrificing classification accuracy.

The primary objectives of this classifier are twofold: first, to detect neural activity associated with specific activity classes, such as different types of limb motion, as demonstrated in this work, and second, to utilize the classification results for closed-loop functional electrical stimulation (FES). The classifier employed in this system distinguishes between three distinct classes of neural pathways, all related to an animal model's hind paw movements: dorsiflexion (hind paw moving upwards), plantar flexion (hind paw moving downwards), or a response to a Von Frey monofilament prick on the heel.

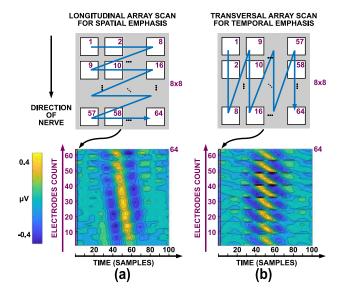

2) Inference model architecture: In the given context, the term "neural pathway" pertains to a small collection of axons exhibiting related functions and firing with approximate synchrony. The neural pathway classifier encompasses the following primary stages: (1) Preprocessing: At the outset, the raw recorded signal originating from each electrode is subjected to filtering and referencing. (2) nCAP detection: The preprocessed signals are averaged signal to enhance SNR, and subsequently, nCAPs are detected by applying a thresholding method to this averaged signal. (3) Spatiotemporal signature

Fig. 9. Illustrations of electrode outputs reorganization (top) and measured spatiotemporal signature representations (bottom) for the cases of: (a) spatial emphasis, and (b) temporal emphasis. Each signature consists of 64 electrode signals (columns) over 100 time-samples (rows), with the electrode outputs being reordered for the purpose of both spatial (a) and temporal (b) emphasis.

extraction: the spatiotemporal signatures of nCAPs are extracted from the preprocessed signal, which serve as inputs for classifier training and evaluation. (4) Training: spatiotemporal signatures, once extracted, are subsequently employed to instruct a CNN model. This is achieved via the utilization of Tensorflow and Keras libraries, with the optimization process being conducted through stochastic gradient descent. Furthermore, the loss function used for this purpose is categorical cross-entropy. The training regimen incorporated 1000 epochs or terminated earlier if no reduction in the validation loss function was observed over the span of 15 consecutive epochs. (5) Classification: Lastly, the classification stage entails the use of extracted spatiotemporal signatures as its input, which in turn associates each nCAP with a specific neural pathway.

The preprocessing is done by using the decimation filter block in the interrogator. Upon identifying nCAPs from the averaged signal, 49 time samples prior to and 50 time samples subsequent to the peak of nCAPs' location were utilized to establish spatiotemporal signatures. As depicted in Fig. 9, the channel scanner sequentially organizes the  $8 \times 8$  digital neural data both longitudinally and transversely, thereby emphasizing the spatial and temporal features, respectively. For each activity type (dorsiflexion, plantarflexion, and heel pricking), the spatiotemporal signatures were assembled using detected nCAPs associated with each stimulus, encompassing M contacts (M = 64 in this example) and T consecutive time samples (T = 100 in this example). This formulation resulted in an  $M \times T$  matrix, representing the spatiotemporal signature for the corresponding nCAP. Next, the two resulting feature maps are fed into the CNN, which is trained to classify the three types of activiting.

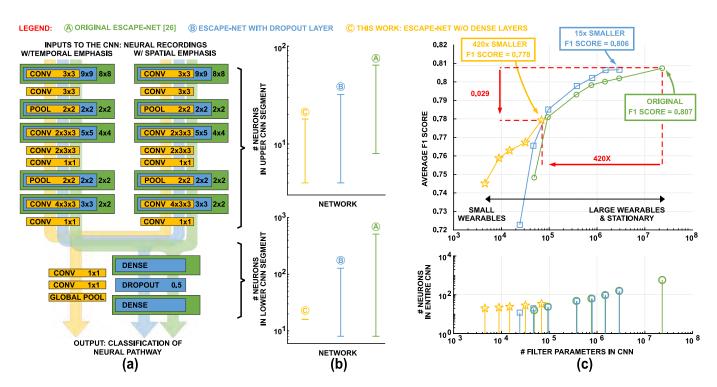

Figure 10(a) compares three CNN architectures: the original ESCAPE-NET (green) [26], a network with a dropout layer (blue), and the reduced network proposed here (yellow). A

#### JOURNAL OF XXXX, VOL. XXX, NO. XXX, XXX 2023

Fig. 10. Performance comparison of three in-the-loop CNN inference engine candidates. (a) Three compared CNN architectures: the original ESCAPE-NET (green) [26], a network with a dropout layer (blue), and the reduced network proposed here (yellow). (b) Distribution of neurons across various layers in the three CNN architectures illustrating the reduced neuron count requirements for the proposed network. (c) F1-score performance curves for the three architectures, highlighting the reduction in the number of filter parameters in the proposed architecture while maintaining comparable performance. This work (yellow) reduces the number of parameters by a factor of 420x compared to [26] (green) while lowering F1-score by only 0.029.

more detailed analysis can be found in one of our recent works [27]. Here, we provide a brief illustration of the proposed network structure and highlight its advantages. The presented CNN is composed of three primary components: convolutional layers, pooling layers, and a global pooling layer. A convolutional layer processes the input image utilizing an  $N \times N$  filter, which traverses the image with a stride of K. The pooling layer consolidates adjacent pixels into a single pixel, yielding an output image with reduced dimensions compared to the input image. Subsequently, the global pooling layer receives the output from multiple convolutional and max pooling layers and generates the classification results. The adopted CNN architecture encompasses two convolutional layers followed by a max-pooling layer, three subsequent convolutional layers, another max-pooling layer, and two additional convolutional layers. The outputs from this sequence are then channeled into two further convolutional layers and one global maxpooling layer. The convolutional layers employ  $3 \times 3$ ,  $3 \times 3$ ,  $2 \times 2 \times 3$ ,  $2 \times 2 \times 3$ ,  $1 \times 1$ ,  $4 \times 3 \times 3$ ,  $1 \times 1$ ,  $1 \times 1$ , and  $1 \times 1$  filters for the first through the ninth convolutional layers, respectively, maintaining a stride length of 1 and zero-padding to preserve the same dimensionality. All max-pooling layers are based on  $2 \times 2$  groupings, and the concluding global pooling layer outputs the three classification results. Figure 10(b) demonstrates the large number of neurons of the green model both in its upper and lower segment, which are directly proportional to the number of parameters (Fig. 10(c, bottom)). This contributes to high model complexity.

determining the type of device which it can be deployed on, as there exists a strong dependance between model complexity and the hardware device's required computational capabilities, memory and power resources. As illustrated in Figure 10(c, green), the green network [26] comprises  $2.5 \times 10^7$  parameters, yielding satisfactory performance with a 0.807 F1-score, as depicted in Fig. 10(c, green curve). Consequently, the hardware implementation is constrained to larger wearable devices or stationary devices, which typically possess more computational resources, memory, and power compared to smaller wearable devices. Deploying this CNN with such an extensive number of parameters on a small wearable device may not be feasible. To accommodate this CNN on a small wearable device, it is essential to significantly reduce the number of parameters. This can be achieved through various techniques, such as network pruning. However, as demonstrated in Fig. 10(c, green curve), reducing the number of parameters used in this CNN results in a significant drop in performance (to F1-score below 0.75).

Figure 10(a, blue) depicts an alternative approach to reduce the dense layer's neuron count by incorporating a dropout layer between the two dense layers. The dropout layer randomly deactivates a fraction of the neurons during training, reducing the number parameters. During inference, all neurons remain active, and the dropout rate scales down the layer's output to maintain expected activation levels. However, reducing parameters in this CNN (Fig. 10(c, blue curve)) also correlates with a decline in performance.

The number of parameters in a CNN is a crucial factor in

The primary contribution in our proposed CNN architecture

#### JOURNAL OF XXXX, VOL. XXX, NO. XXX, XXX 2023

is to replace the output's fully connected layer with two convolutional layers, followed by a global pooling layer. This reduces parameters while maintaining performance. This "fully convolutional" technique, common in state-of-the-art CNN architectures [28], maps input spatial dimensions to the desired output classes using convolutional layers. The initial layer captures higher-level features, while the subsequent layer focuses on mapping these features to the output classes. After the convolutional layers, a global pooling layer is introduced. It aggregates feature maps by computing the maximum value (global max pooling) across each map's spatial extent. This yields a single value per map, interpreted as a "confidence score" for each class. The global pooling layer's output is a 1D vector containing confidence scores for all classes (e.g., three movements). These scores pass through a softmax activation function to obtain final class probabilities. This proposed architecture reduces parameters by eliminating the fully connected layer, preserving classification capabilities. Advantages include a more compact, computationally efficient model, improved generalization from the global pooling layer's spatial invariance, and support for variable input spatial dimensions.

Figure 10(c) demonstrates that the proposed classifier achieves a significant reduction in the number of filter parameters, decreasing them by a factor of 420, while only incurring a modest decline of 0.029 in the F1-score performance. Results are based on the dataset provided in [26] for nine rodents. This outcome emphasizes the classifier's reduced size without substantially compromising its overall performance, establishing it as a vital component within a low-power PNS neural interface system.

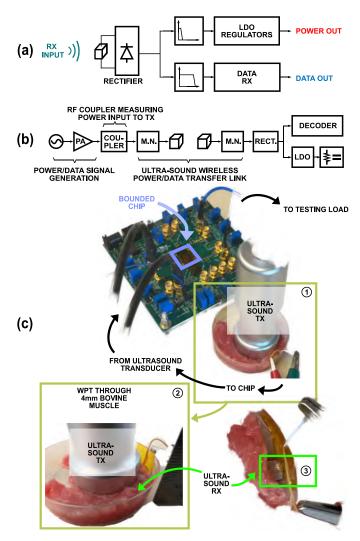

## E. WPT and data receiver

Wireless power transfer (WPT) techniques are essential for powering implantable biomedical devices, providing numerous benefits such as the elimination of wires, enhanced device longevity, and a decreased risk of infection. Various methods have been proposed for this purpose. Inductive coupling [29] is a well-established and widely-used method that achieves moderate power transfer efficiency with a relatively simple design and implementation. However, it has a limited range, typically a few millimeters to centimeters, and its performance is sensitive to coil misalignment. Magnetic resonance coupling [30] offers a longer range compared to inductive coupling (up to several times the coil size), higher power transfer efficiency, and increased tolerance to coil distance variations. However, it requires a more complex design and implementation, and larger coils for efficient power transfer. Furthermore, the strong electromagnetic interference it generates could potentially affect other electronic devices. The capacitive coupling method [31], while characterized by a simple design and low cost, is limited by its range, low power transfer efficiency, and sensitivity to tissue and environmental changes.

In the context of peripheral nerve implants, ultrasonic power transfer [32] has emerged as a particularly promising candidate. This method can achieve high power transfer efficiency and superior delivery depth with minimal impact from the presence of biological tissue. Moreover, it does not generate

Fig. 11. The PNS neural interface wireless power experimental measurements. (a) Power RX architecture. (b) Wireless power measurement setup components. (c) Experimental setup of ultrasound wireless power transfer through bovine muscle.

electromagnetic interference, making it compatible with the sensitive electronic components used in such implants. Despite its sensitivity to misalignment, the benefits of ultrasonic power transfer render it highly suitable for powering peripheral nerve implantable devices. Specifically, we chose ultrasonic powering over inductive powering because of its deeper penetration capabilities and absence of electromagnetic interference, the factors we believe are crucial for the successful application in peripheral nerve implants. Consequently, the proposed PNS neural interface has been designed to ensure compatibility with ultrasonic energy harvesters, facilitating wireless energy transmission through the skin. Ultrasound power is transmitted from the wearable interrogator, and the power waveform contains serialized commands modulated in the amplitude. In the current study, the experiments were conducted on an anesthetized rat as the test subject. Due to the anesthetization, the issue of angular misalignment resulting from natural movements was not applicable. Therefore, this study does not account for potential effects of angular misalignment, a factor

© 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

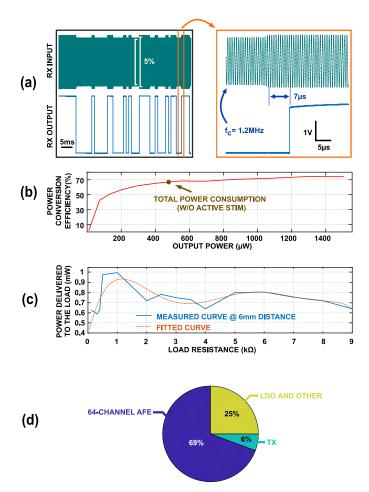

Fig. 12. (a) Data receiver demodulating a 1.2 MHz PRBS-modulated ASK power waveform with a 5% modulation index. (b) Power conversion efficiency versus output power for rectifier and LDO circuits. (c) Power delivered ex vivo to varying load resistances at a 6 mm distance through cow muscle tissue. (d) Power breakdown of the proposed design.

that should be considered in future research involving mobile or conscious subjects.

As illustrated in Fig. 11(a), the on-chip ultrasound power receiver is interconnected with the power and data-receiving circuits. The power path comprises a full-wave bulk-biased passive rectifier, accompanied by a narrowband low-pass filter, followed by a low-dropout (LDO) voltage regulator bank. The data receiver receives amplitude-shift keying (ASK)modulated data and subsequently forwards it to another lowpass filter. This filter's cutoff frequency is determined based on the data rate of the transmitted ASK signal, ensuring that it effectively permits the desired frequency components associated with the data to pass while attenuating undesired high-frequency components. Once the low-pass filter has been applied to the received ASK signal, the resulting output is a smoothed rendition of the original baseband data. This filtered signal is then processed by a decision-making circuit, such as a Schmitt trigger that is used in this work, to recover the binary data transmitted via the ASK modulation scheme. This approach enhances the overall performance and reliability of the PNS neural interface, ensuring efficient wireless communication and energy harvesting capabilities for implantable biomedical devices.

Figure 11(b) presents the wireless power measurement setup, consisting of a function generator and a power amplifier responsible for generating the pseudo-random binary sequence (PRBS) data and power essential for wireless ultrasound powering. A coupler is employed to measure the power directed into the matching network and ultrasound transmitter (TX) transducer. The ultrasound receiver (RX) transducer is followed by the matching network, which receives data and power to be fed into the rectifier for rectification. Subsequently, the rectified signals are supplied to the LDO voltage regulator and data demodulator for voltage regulation and data decoding, respectively. The selection and arrangement of these components have been planned to ensure the accuracy and reliability of the measurements conducted in the wireless power transmission system.

Figure 11(c) displays detailed images of the experimental setup. In this configuration, the chip is wire-bonded directly onto the PCB using a chip-on-board technique to minimize parasitic effects. The received ultrasound power is captured by a 4mm x 4mm ultrasound RX and subsequently directed to an on-chip power rectifier for both powering and data transmission. The ultrasound power is transmitted through a 4mm-thick layer of bovine muscle.

The TX component is designed to be in direct contact with the skin, eliminating the air gap and thereby minimizing power reflection issues. This means that the distance between the TX and RX components is solely determined by the depth at which the RX is implanted.

Figure 12(a) showcases the successful demodulation of a PRBS-modulated ASK power waveform at a frequency of 1.2 MHz, with a modulation index of 5%. This outcome signifies the efficacy of the data receiver in processing the ASK power waveform.

Ultrasound power transfer systems, typically achieving efficiencies in the realm of tens of percent, underscore the critical role of conversion efficiency in wireless power transfer. Figure 12(b) provides the measurement result of the power conversion efficiency in relation to the output power for the power-shaping circuits, which include the rectifier and LDO. These circuits demonstrate a power conversion efficiency of 70% at the nominal load of 480  $\mu$ W, which corresponds to the system's nominal power consumption in the absence of active stimulation.

Figure 12(c) exhibits the amount of power delivered to the load with varying resistance levels at a distance of 6 mm through cow muscle tissue positioned between the power transmitter (TX) and the power receiver (RX). This illustration emphasizes the effectiveness of the power management unit and the data receiver in maintaining consistent power delivery and data reception under challenging conditions, such as the presence of biological tissues.

Lastly, a pie chart detailing the power distribution among various components is included in Fig. 12(d). The total power requirement for the implant to be functional is  $480\mu$ W. This is broken down as follows: (1) 64 analog frontends -  $5.2\mu$ W each, (2) transmitter -  $27.63\mu$ W at a 20 Mbps operation

JOURNAL OF XXXX, VOL. XXX, NO. XXX, XXX 2023

A: DORSIFLEXION 2uVrms CONFUSION MATRIX 100% 10µ\ (a) DORSIFLEXION TEMPORAL EMPHASIS EXAMPLE DORSIFLEXION SPATIAL EMPHASIS EXAMPLE B: PLANTARFLEXION 2µVrms в С (b) ACTUAL RESULTS FOR 3-FOLD DATASET FOR ONE ANIMAL PLANTARFLEXION SPATIAL EMPHASIS EXAMPLE PLANTARFLEXION TEMPORAL EMPHASIS EXAMPLE 1s C: HEEL PRICK MEAN 2µVrms SD ACCURACY 86.7% 6.0 % F-1 10µ\ 85.6% 7.0 % (c) SCORE (f) HEEL PRICK SPATIAL EMPHASIS EXAMPLE HEEL PRICK TEMPORAL EMPHASIS EXAMPLE DUTY CYCLE OF APPLIED SE (d) MECHANICAL (e) RESULTS INPUT FOR: B, & C

Fig. 13. (a-c) In vivo rat sciatic nerve recordings experimental results showcasing naturally evoked compound action potentials nCAPs resulted from three distinct hind paw stimuli: (a) dorsiflexion, (b) plantarflexion, and (c) heel prick, along with their corresponding spatiotemporal signatures, used as inputs to the CNN classifier. (d) The corresponding time-aligned mechanical displacement/stimulus rhythm. (e) A simplified architecture of the CNN classifier shown in Fig. 9(a, yellow). (f) Classifier performance: 86.7% accuracy and 85.6% F-1 score obtained from one rodent. (The classification results in (f) are from a different data set, not from recordings in (a), (b), and (c)).

frequency, (3) LDO banks and other -  $119\mu$ W, (note: This power analysis does not include the stimulator, which is only activated occasionally, or the optional RISC-V processor for on-chip data processing).

In summary, the comprehensive wireless power measurement results presented herein serve to underscore the robustness and efficiency of the power management unit and data receiver within the PNS neural interface system. These components have been designed and optimized to ensure reliable performance, even in the presence of biological tissues and varying load conditions, making them essential to the overall functionality of the system.

## V. IN VIVO EXPERIMENTAL RESULTS

The previous section provided a comprehensive discussion on the implementation details of the PNS neural interface integrated circuit (IC), including key measurement results for each individual block. This section focuses on the in vivo experimental results obtained from a Wistar rat during the course of this study.

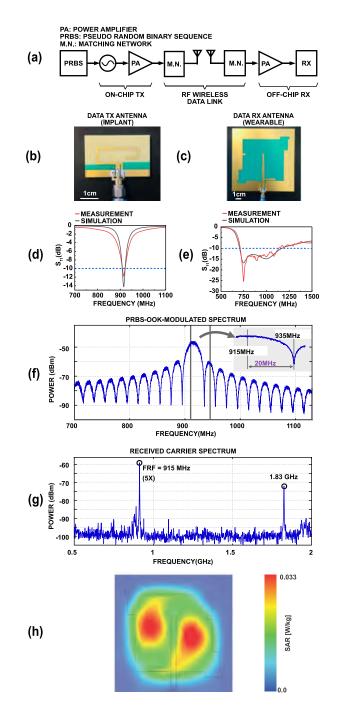

The IC was validated in vivo by conducting sciatic nerve recordings from an anesthetized rat. A flexible, high-density 8x8-contact polyimide cuff electrode array was implanted over the sciatic nerve and connected to the IC. Figure 13 (a-c) displays the recordings obtained by the IC, capturing compound action potentials naturally evoked by three distinct rat paw movements: dorsiflexion, plantarflexion, and heel prick, as displayed in Fig. 13(a, middle), (b, middle), and (c, middle), respectively. These movements engage different neural pathways, underscoring the versatility and sensitivity of the IC in detecting diverse nerve activities. The recordings are subsequently passed from the IC to the neural pathway classifier, implemented in the wearable digital interrogator.

14

Spatiotemporal signatures derived from the recordings of the cuff electrode array serve as inputs for the convolutional neural network (CNN) classifier. These signatures include dorsiflexion, plantarflexion, and heel prick spatiotemporal signatures, as shown in Fig. 13(a, right), (b, right), and (c, right), respectively. The spatiotemporal signatures are fed into the aforementioned CNN classifier, as depicted in Fig. 13(e). Finally, the classifier identifies the specific neural pathway corresponding to each sample, showcasing its ability to accurately and reliably classify the input data.

As demonstrated in Fig. 13(f), the classifier exhibits an accuracy of 86.7% and an F1 score of 85.6% from a 3-fold dataset derived from a single animal. The experimental results indicate that the compound action potentials associated with distinct neural pathways are effectively captured by the IC, enabling the classifier to differentiate between these pathways based on the recorded nerve activity. This differentiate

#### JOURNAL OF XXXX, VOL. XXX, NO. XXX, XXX 2023

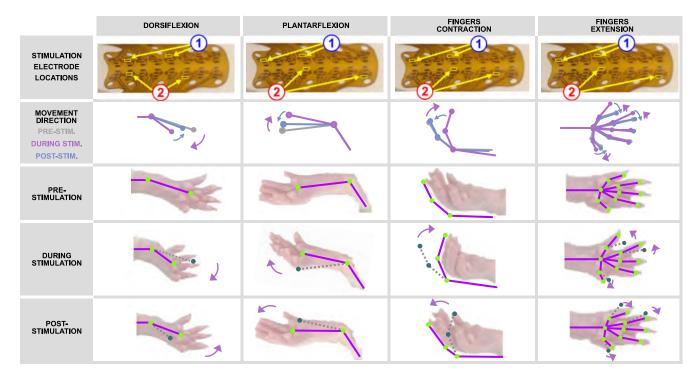

Fig. 14. Experimental in vivo validation of fascicle-selective stimulation in a rat using TIS, demonstrating the capability of the system to activate distinct neural pathways by choosing specific electrode pairs. This figure depicts positions of the four different rat's hind paw movement types during pre-stimulation, stimulation, and post-stimulation phases, respectively.

tiation capability is crucial for identifying and distinguishing the neural pathways responsible for specific movements or actions, enhancing the potential applications of the PNS neural interface system.

In the context of implantable PNS interfaces, the choice of classifier—whether external or on-chip—significantly impacts the overall power consumption. Although on-chip classifiers offer the advantage of localized data processing, they require a substantial power budget comparable to using our low-power transmitter (27uW) to send all the data off-chip. We refer to the energy-efficient neural classifiers presented in [33], [34] for comparative benchmarks.

In this work, we focus on utilizing an external classifier due to the comparable power consumption and the scope of our study. The employment of an external classifier could introduce latency concerns, such as delays due to wireless transmission and external processing. To provide a clearer understanding, preliminary tests indicate that the wireless link latency is less than 1 ms, while the classification latency is around 10 ms. These figures suggest that the system is capable of real-time performance within acceptable ranges for many PNS applications. Nevertheless, further investigations on latency considerations will be the subject of future work.

Figure 14 displays the results of the selective stimulation achieved during in vivo experiments, demonstrating the capability of the system to activate distinct neural pathways by choosing specific electrode pairs through temporal interference stimulation (TIS). The first row in Figure 14 exhibits the four induced movement classes. The second row illustrates the corresponding stimulation electrode locations, while the third row presents the stick diagrams of the rat's hind paw movement direction during the pre-stimulation, stimulation, and post-stimulation phases. Rows four, five, and six depict the rat's hind paw location along with the stick diagrams during pre-stimulation, stimulation, and post-stimulation phases, respectively.

In the in-vivo experiments, the stimulation current amplitude was set to approximately 2.4 mA. The blue electrode pair was set to a stimulation current frequency of 2 kHz, while the red electrode pair operated at a frequency of 2.005 kHz. This resulted in a beat frequency of 5 Hz, leading to observable movement in the rat's hind paw. This selection process elicits a variety of movements, including dorsiflexion, plantar flexion, and distinct finger movements such as contraction and extension. The process of selecting electrode pairs for stimulation was carried out through a trial-and-error approach. Following the stimulation, the rat's hind paw demonstrates differentiated movement, indicating the effectiveness of the system in modulating neural activity. The presented results highlight the potential of the proposed PNS neural interface for facilitating precise stimulation and manipulation of neural pathways.

The in vivo experimental outcomes highlight the successful implementation and integration of the IC with a flexible, highdensity polyimide cuff electrode array for selective recording of sciatic nerve activity. The IC's capability to detect compound action potentials from various neural pathways during distinct limb movements emphasizes its versatility and sensitivity in capturing a diverse range of nerve activities. Furthermore, the neural pathway classifier, deployed within the wearable digital interrogator, demonstrates exceptional accuracy and reliability in differentiating between neural pathways based on the recorded nerve activity. The stimulation results further substantiate the system's selective stimulation capabilities.

This work emphasizes the potential of the PNS neural interface system to provide accurate, reliable, and efficient monitoring and control of neural activity in a variety of biomedical applications. The successful development and validation of a PNS interface capable of selectively stimulating and recording neural activity in vivo not only lays the foundation for future research and applications in the field of fascicleselective neural interfaces but also opens up possibilities for advancements in neuroprosthetics, neuromodulation and other areas of neuroscience.

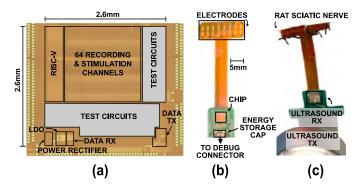

Fig. 15. (a) Die micrograph of the 65nm CMOS chip (2.6x2.6 mm<sup>2</sup>). (b-c) PNS interface microsystem form factor illustration: (b) top view showing a rigid-flex PCB with wire-bonded die, an energy storage capacitor, and 64-contact electrode array; and (c) bottom view, showing ultrasound piezo receiver and an example of cuff electrode placement on a rat sciatic nerve.

## VI. COMPARISON TABLE AND SUMMARY

The die micrograph, displayed in Fig. 15(a), demonstrates that the chip fabricated utilizing a 65nm CMOS process node encompasses an active area of  $2.6 \times 2.6$  mm<sup>2</sup>. For the purpose of demonstrating the achievable form factor, our latest active PNS neural interface prototype has been realized through a rigid-flex printed circuit board (PCB) design. The rigid portion of the PCB houses the wire-bonded die and an energy storage capacitor, which is responsible for delivering the stimulation charge, as illustrated in Fig. 15(b). Conversely, the flexible segment accommodates the 64-contact gold-plated electrodes, which interface directly with the nerve. A bottom view of the PNS interface, depicted in Fig. 15(c), exhibits the ultrasound piezo receiver and the cuff electrode wrapped around a rat's sciatic nerve.

When benchmarked against recently published PNS interfaces as described in Table I, the current work offers several notable advantages. Having the wireless powering capability, it provides the highest number of recording and stimulation channels while consuming nominal power of  $480\mu$ W and occupying an area of merely 5 mm<sup>2</sup>. Furthermore, it is one of the few PNS interfaces that feature data transmission capabilities, boasting an energy efficiency of 1.38 pJ/bit. Moreover, this work presents one of the few PNS interfaces with stimulation capabilities, delivering a larger current range and voltage compliance compared to previous studies. In terms of performance metrics, it surpasses other front-ends from recent PNS research by achieving the smallest noise efficiency factor of 3.93 (including the ADC power) and attaining the largest Schreier figure of merit of 173.4 dB.

In summary, this study introduces an advanced PNS neural interface that stands out among the existing solutions due to several innovative design elements and functionalities. Firstly, it employs a minimally invasive approach, mitigating the risk of nerve damage or tissue inflammation that may arise from more invasive techniques. This feature is crucial in ensuring patient safety and comfort during long-term therapy. Secondly, the fully-wireless operation capability of the proposed interface reduces the overall size of the device and eliminates the need for periodic battery replacements, further enhancing its practicality for chronic use.

Another aspect of the proposed PNS neural interface is the incorporation of a wearable interrogator with integrated machine-learning capabilities. This feature could allow the device to adapt to the patient's specific needs and optimize the neuromodulation therapy accordingly, thereby improving the efficacy of the treatment.